GPS-Disciplined Oscillator

GPSDO Drives Electro-Mechanical (Analog) Clock

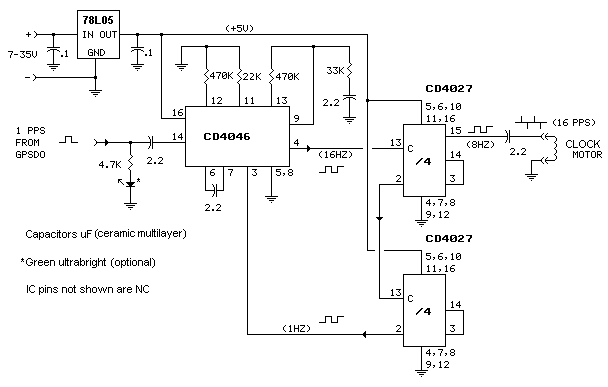

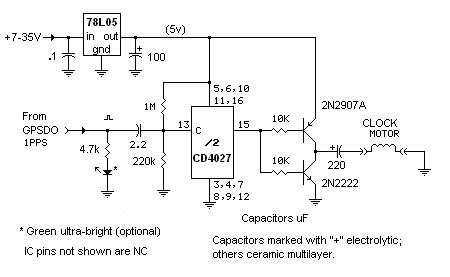

Circuit converts unipolar GPSDO output to bipolar clock motor drive signal.

Max Carter

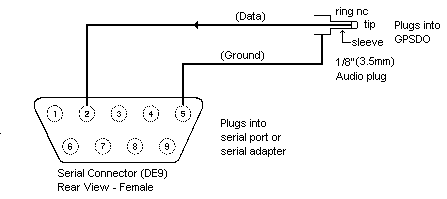

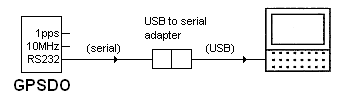

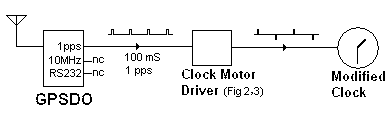

A GPS-disciplined oscillator (GPSDO) provides precisely timed 100 mS unipolar (3.3V) pulses at one-second intervals (1 pps), synchronised to Coordinated Universal Time (UTC). A GPSDO can be had for around $100 from eBay.

The pulses can be used to synchronize an ordinary $10 battery-powered (minus the battery) clock movement. Two circuits are shown. Figure 2 supports 1 pps, non-continuous sweep (stepped) movements, Figure 3 supports continuous sweep movements.

Figure 1

Figure 2

(stepped movement)

The input pulses from the GPSDO drive a CMOS CD4027 dual flip-flop (only one section is used). The flip-flop delivers a symmetrical 0.5 Hz square wave to the half-bridge driver circuit made of complementary (PNP/NPN) transistors. The output from the half-bridge is coupled to the clock motor through the 510Ω voltage dropping resistor and the 150 µF coupling capacitor. The circuit delivers alternating (positive/negative) 100 mS pulses to the clock motor. The circuit requires positive DC power in the range of 7-35 volts. It can be powered from the same source (wall wart) that powers the GPSDO.

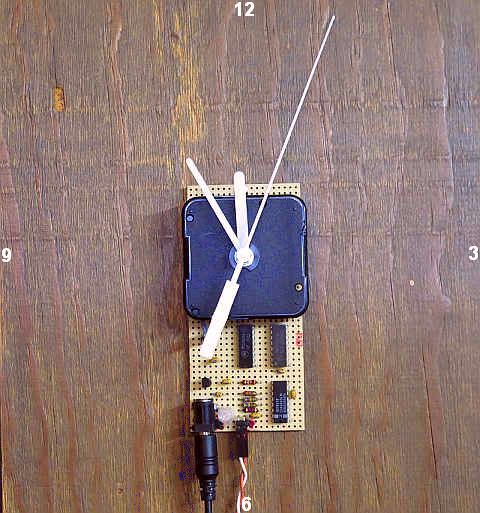

As Built

Clock Modification - Connecting to the Motor Winding

- Disassemble the clock to gain access to the solder pads on the circuit board where the motor winding is connected. Be sure to note the order in which the wheels (gears) are removed.

- Using a utility knife or small hand grinder, cut one of the traces on the circuit board so as to isolate the winding from the on-board circuitry.

- Tack solder a length of AWG 28 (.08mm2) two-conductor wire to the pads.

- Route the wire to the outside of the motor case.

- Reassemble the clock. It's not necessary to reinstall the battery.

- Reinstall all hands pointing at 12. Verify the hands are parallel and not touching. Do not reinstall the plastic face cover (if there is one). You will need access to the hands for initialization.

Initialization

Initialization is done manually. Go to Official U.S. Time or other UTC source. With the clock running, move the minute and/or second hand as necessary until the clock displays the correct time. Do not force the hour hand. The clock will continue to tell the correct time to the second unless power is interrupted.

Installed

The GPSDO is on the left. The converter/driver is in the white plastic box on the right.

Circuit Accommodates Sweep-Style Movement

Most bare quartz clock movements available today for repair or DIY are of the "sweep" persuasion. Rather than moving in one-second steps, the second hand moves continuously and steadily. This circuit converts the 1 pulse per second output from the GPSDO to a 16 PPS bipolar drive signal to spin the clock's two-pole motor at 8 revolutions per second (480 RPM). The movement's gear train reduces the 480 RPM motor speed to 1 RPM second hand speed.